|

本公司具有根据用户的指标要求提供多种解决方案的实力。本公司的PLL频率合成器产品具有低相噪,低杂散,捷变频等特点。

该系列产品包括:

整数分频单环PLL频率合成器;整数分频混频环PLL频率合成器;

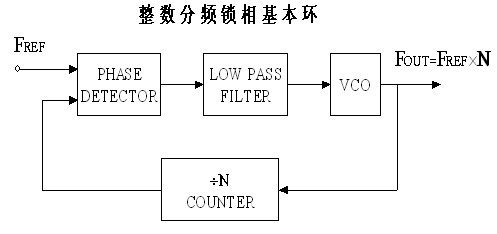

整数分频单环PLL频率合成器系列产品采用具有极低相位噪声基底的整数分频锁相环芯片,用单环实现频率合成。产品电路简单、体积小、重量轻,集成度高,但具有较高的性能指标。公司可按用户要求来设计电路以满足其对指标的特殊要求。当放宽对杂散抑制的要求和采取特殊电路措施,跳频时间可以做得更短。由于整数分频单环PLL频率合成器方案的自身特点决定了跳频步进和相位噪声的矛盾,要想进一步提高相噪指标,必须采用混频锁相方式。

下表为整数分频单环PLL频率合成器的典型指标。

|

频率

范围

(GHz) |

相位噪声Tpy。

dBc/Hz@ |

输出功率

(dBm) |

谐波抑制

Tpy。

(dBc) |

杂波抑制

Tpy。(dBc) |

步进

Tpy。

(MHz) |

跳频时间

Tpy。

(us) |

|

1kHz |

10kHz |

|

P波段 |

95 |

100 |

10 |

30 |

70 |

2 |

15-50 |

|

L波段 |

90 |

95 |

10 |

30 |

70 |

2 |

15-50 |

|

S波段 |

90 |

95 |

10 |

30 |

70 |

5 |

15-50 |

|

C波段 |

85 |

90 |

10 |

30 |

70 |

10 |

15-50 |

|

X波段 |

80 |

85 |

10 |

30 |

65 |

10 |

15-50 |

|

Ku波段 |

75 |

80 |

10 |

30 |

60 |

10 |

15-50 |

|

Ka波段 |

70 |

75 |

10 |

30 |

55 |

10 |

15-50 |

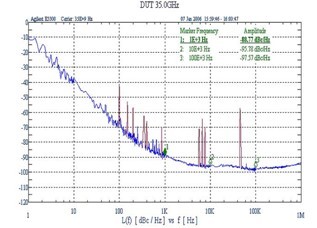

注:以上PLL典型产品带宽在2%-50%之间。全部采用整数分频锁相基本环方案得到的指标。采用具有低相位噪声基底的整数分频 PLL 频综芯片,用单环实现频率合成。产品电路简捷、尺寸小,但仍具有很高的电气指标。

频综组件

采用低相噪的全数字锁相环芯片和表贴元件,用混频环/多环方案实现小步进、低相噪锁相频综组件,组件有单路输出和异频多路全相参输出两种选择。利用倍频器可将低噪声的微波频综源扩展到所需要的任意频段,保留了相噪、低杂散和多点输出的特性并拓宽了频带宽度。

|

频率

范围

(GHz) |

相位噪声

dBc/Hz |

输出

功率

(dBm) |

谐波

抑制

(dBc) |

杂波

抑制

(dBc) |

步进

(MHz) |

跳频

时间

(us) |

|

10kHz |

100kHz |

|

8.75±0.25 |

-103 |

-104 |

10 |

-40 |

-60 |

2.5 |

<20 |

|

35±0.2 |

-95 |

-97 |

10 |

-40 |

-55 |

<2 |

<20 |

|

94±1.5 |

-77 |

-80 |

-5 |

-40 |

-50 |

40 |

<20 |

注:以上为公司部分频综组件的典型指标,我公司可根据用户的要求进行定制。 |